劉承瑋

2021/7/8

摘要

半導體產業在我國經濟的影響日益增加,在全球晶片產出佔比超過百分之六十,從晶片製造除了設備部分主要來自荷蘭,從上游的設計、材料到下游的製造、封測在台灣都已具備完善的產業鏈。全球晶片製造產業中,我國在先進半導體製造技術有相當的領先地位。本篇報告將會探討半導體製程技術的技術發展與各種技術分類說明,以及半導體工業之污染與廢棄物處理方法。

關鍵字: 半導體、半導體製程技術。

1. 前言

半導體可以說是現在電子產業的根基,應用於電子產品上,主要進行著核心運算及各種高級的功能,電子產品涵蓋了資訊、通訊、各種消費性電子產品、工業用產品、國防太空等等。半導體的電阻是一種介於導體與非導體之間的材料,最常見的為矽,是電子裝置的基本零件之一,為了使電腦能執行基礎的邏輯運算,電路必須能夠以電控來進行開關,也就是電晶體,而電晶體就需要運用到半導體的性質來進行設計,由此可以看見半導體的重要性,其技術的創新更是驅動電子產品功能進步的原動力,因此大多國家都以半導體工業為優先發展目標,台灣也不例外。

2. 半導體發展與簡介

2.1 歷史發展

現今的許多半導體裝置是由真空管演變而來,其中真空管發明中較具影響力的是由Lee De Forest所發明的三極真空管,它用來放大電訊號,含有兩個電極和一個簾柵極(grid)。後來演變出固態電晶體(soild-state transistor),與真空管有相同的電功能,優點有尺寸小、不需真空、穩定性高、重量輕以及耗損低。之後,矽材料電晶體邁入商用化進程,逐漸取代真空管,其中第一個商用化的平面電晶體是由鋁製內連線層沉積於矽晶圓表面,以熱氧化法成長氧化層以作為鋁製導體之絕緣,如此使用金屬層與氧化層是平面化技術(planar tech)的關鍵。

2.2 積體電路積體電路(integrated circuit)是集合許多電子組件

於單一矽基板的構造,然而最早半導體材料是以鍺(Ge)為基板(substrate),元件由獨立電線連接,再成長氧化層作為絕緣,分隔不同矽元件金屬導體。

2.3 半導體趨勢

2.3.1 增加晶片特性

當晶片元件愈小,晶片間距愈短時,使電訊號通過電路電路的時間縮短,也就是增加晶片速度(chip speeding)。

2.3.2 縮小臨界尺寸

晶圓上最小的特徵尺寸(feature size)稱為臨界尺寸(critical dimension),也就是最小線寬。

2.3.3 微縮化(scaling)

將晶片上的元件同步縮小(coordinated shrinking)。

2.3.4 提升可靠度(increase in chip reliability)

提升有效期限內可正常運作的能力,也就是提升晶片的壽命,可藉由降低灰塵、雜質達成。

2.4 半導體材料特性

2.4.1 固態能帶理論(Energy-Bond Theory of Solid)

一般狀態時,電子處於價電帶中,當電子吸收能量而躍遷到導電帶中就會導電。首先,絕緣體的導電帶和價電帶之間存在較大的能隙(energy gap),電子跳到導電帶的能量要很大。而半導體的能隙較小,只需施加一點能量就能導電。至於導體則是導電帶和價電帶重疊,所以電子一直在導電帶中。另外,導電率(conductivity, C)和電阻率(resistivity, )只和材料特性有關,無關幾何形狀,並且有反比關係

而電阻(resistance, R)則和材料特性及物理幾何形狀有關

2.4.2 常用於晶圓製造的元素族群1. IIIA (B, Al, Ga, In, Tl) :用於參雜半導體材料(主

1

要是用B),增加電洞數產生P型半導體。

2. VA (N, P, As, Sb, Bi):用於參雜半導體材料(主要是P, As),增加電子數產生N型半導體。

若要使P型半導體和N型半導體達到相同導電率,N型參雜所需的濃度較低,因為移動電子所需的能量比移動電洞還小。

3. VIIA (F, Cl, Br, I, At) :利用其腐蝕性來蝕刻、清洗。

2.4.3 本質矽與外質矽

最初半導體材料採用的是鍺(Ge),之後因矽的含量多、熔點較高和操作溫度範圍大而取而代之。純矽又稱為本質矽(intrinsic silicon)且不會導電,反之,有經過參雜加入參質(dopant)可提升導電率,稱為外質矽(extrinsic silicon)。

2.4.4 其他半導體材料

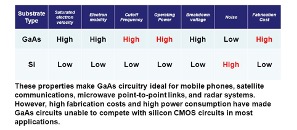

最主要的化合物半導體為III-V族,如砷化鎵(GaAs),砷化鎵半導體的優點有電子移動速度快,縮減其寄生電容、降低訊號訊號失真、高電阻率、抗輻射能力佳,缺點為缺乏自然氧化層,因而限制MOS元件發展,且材質脆弱、含量少。另外還有氮化鎵,用於製作藍光二極體、藍光雷射。至於第二大類的化合物半導體為II-VI族,主要是碲化鎘(CdTe),用於製作紅外線偵測系統,還有硒化鋅(ZnSe),用於藍光LED。

圖一:砷化鎵半導體的優點

2.4.5 矽的晶體結構

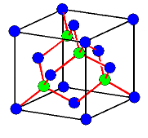

多個原子呈現重複排列的形狀稱為晶體(crystal),晶格(lattice)則表示晶體結構內原子排列的特徵。另外,在一堆重複排列中,最簡單有序的原子排列即為單位晶胞,而矽的單位晶胞為具有面心立方之鑽石結構(FCC diamond structure)。

圖二: FCC diamond structure

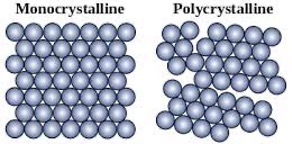

另外矽還有單晶、多晶結構。

圖三:單晶、多晶結構圖

3. 積體電路製造

積體電路製造主要包含以下五個階段:晶圓準備(wafer preparation)、晶圓製造(wafer fabrication)、測試/分類(test/sort)、裝配和封裝(assembling and packaging)、終測(final test)。

3.1 晶圓準備(wafer preparation)

此步驟包含結晶(crystal)、長晶(growing)、圓柱化(rounding)、切片(slicing)、研磨(polishing)。

結晶、長晶這步驟是把半導體級矽(semiconductor-grade silicon)轉化成單晶矽晶棒(ingot),而半導體級矽製備最主要的方式是西門子製程法(Siemens process),西門子製程是在流體化床中將純度98%以上的冶金級矽(Metallurgical-grade silicon)和HCl、SiCl4、H2進行反應:

Si+3HCl SiHCl3+H2

再進行蒸餾純化出SiHCl3,接著加氫還原成高純度多晶矽,最後再利用CVD法(chemical vapor deposition)沉積:

SiHCl3+H2 Si + 3HCl

雖然西門子製程已經發明已久且消耗成本龐大,但是現今仍然沒有發展出能夠產出相當或超過西門子製程產出之純度99.999%以上之矽的製程,所以現在約75%半導體廠還是使用西門子製程。

圖四:西門子製程

而將半導體級矽轉化成單晶矽的結晶成長方法主要有兩種,分別是CZ法(Czochralski method)和浮動區域法(floating zone technique)法。

2

CZ法是將多晶半導體級矽放入鉗鍋(crucible)以電阻加熱器、射頻加熱線圈將融化矽成液狀矽融湯再將晶種(seed, 是一小塊單晶,其晶體方向和矽晶錠預定生長方向相同)接觸融化的矽,以和鉗鍋旋轉方向相反的轉向旋轉並向上拉升生成矽晶錠。

圖五:CZ法示意圖

FZ法則是將晶種和多晶柱連接至於灌入鈍氣的鍋爐旋轉,再用活動式射頻線圈加熱,線圈會由單晶部分開始往多晶棒移動,經加熱過的矽就會變成單晶矽。此法製作的矽晶錠有高純度且含氧量最低。

圖六:FZ法示意圖

接下來會進行矽晶錠的修剪、端點移除、直徑研磨,使矽晶錠變成工整的圓柱體,再形成主平面(flat grinding)以及晶圓切片(wafer slicing),就製造出一片片有缺口的圓形晶圓薄片。隨後要進行邊角磨光(edge rounding),把邊緣打圓使受力分散,降低因邊緣碰撞造成晶圓損害的可能性。然後會進行晶圓表面的研磨(lapping)和蝕刻(wafer etching)清除雜質,再進行表面的拋光(polishing),最後進入晶圓檢視。

圖七:晶圓準備流程

3.2 晶圓製造(wafer fabrication)

此步驟包含清洗(cleaning)、加層(layering)、製作佈線圖案(patterning)、蝕刻(etching)、參雜(doping)等。以下會以CMOS製程說明。

首先會加入氧氣使矽基板(也就是晶圓片)氧化產生場氧化層(field oxide),然後旋轉矽基板進行光阻旋塗,以利用離心力均勻塗佈光阻,接下來進行晶圓對準與曝光,將光罩(有圖案的不透光鉻膜)對準晶圓再用紫外光照射光阻,接著用顯影劑洗掉因被曝光而改變結構性質的光阻,再用電漿進行氧化層蝕刻,去除氧化層後,用氧電漿去除光阻(photoresist strip),再加入氧氣形成閘極氧化層,然後進行多晶矽沈積、多晶矽光罩及蝕刻、光阻光罩及蝕刻,接著再進行離子植入,把3A或5A元素打入基板形成外質矽並去除光阻,然後進行氮化矽沈積,此氮化矽層為最上層,又稱為保護層(passivation layer)可防止水氣、刮傷和污染,最後蝕刻出接觸窗,再沈積金屬和蝕刻。

圖八:CMOS製作流程示意圖

3

上述製作外質矽的步驟,也就是雙井製作步驟(twin well process)可由以下n井形成步驟說明,第一步會在晶圓上長出一層磊晶層(epitaxial layer growth),磊晶層是一層非常純淨的矽層,稍微參雜p型參質,可控制參雜濃度和形式。第二步是初始氧化層成長(initial oxide growth),將晶圓清洗、移除自然氧化層,放入攝氏一千度的爐管形成氧化層,以保護磊晶層,防止離子植入時對矽的傷害、控制參質參雜深度。第三步是第一道光罩n井植入(1st mask n-well implant)。第四步是n井離子植入,晶圓上有光阻塗蓋的地方可對離子植入做保護,高能正離子從光阻之窗口或開口穿透入磊晶層表面。第五步是退火(anneal),金屬加熱再冷卻,以增加延展性和韌性。

圖九:n井形成步驟示意圖

3.3 測試/分類(test/sort)

此步驟包含探測(probing)、測試、分類。標示出有缺陷的晶片。

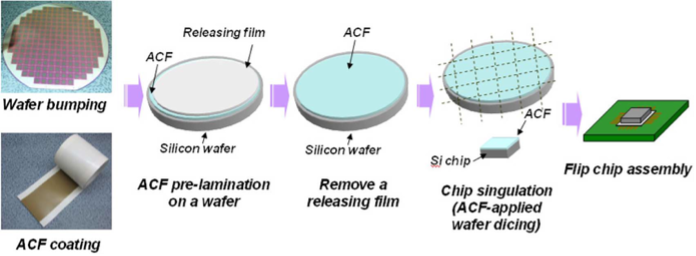

3.4 裝配和封裝(assembling and packaging)

研磨晶圓背面使基板厚度降低,並貼上乙酸乙酯膠帶防止切割時產生移位,在沿切割線(scribe line)切割晶圓,分離每個晶粒,再將晶粒黏於封裝體內,並作金屬打線。

圖十:裝配和封裝圖

3.5 終測(final test)

確定晶片通過電子和環境測試。

圖十一:晶圓製造後期流程圖 4. 晶圓製造技術說明

上個部分已概述積體電路製造流程及步驟,以下將詳述其中晶圓製造的各種技術。

4.1 氧化(oxidation)

氧化層以成長(grow)或沉積(deposit)的方式生成,成長是將晶圓暴露在高溫、高純度的氧中反應,此高溫製程是在擴散區進行,氧化物是從矽導體長出且消耗部分的矽,故稱成長。沈積則是用外加的矽和氣反應,再形成上晶圓。本節只針對熱成長說明,暫時不討論以沈積方式生成氧化層,下個部分會說明沈積的所有機制與作用。

4.1.1 氧化層薄膜(oxide film)

成長氧化層其熱氧化溫度在700~1100 °C,長出的氧化層稱為熱氧化層(thermal oxide)或熱二氧化矽(thermal silicon dioxide, SiO2),熱二氧化矽是介電材料,無法導電,熔點為1732°C。在熱成長時會有幾層單層原生氧化層形成,甚至在25°C時此原生氧化層會增厚40Å,原生氧化物是不均勻的,且有雜質。

4.1.2 氧化的化學反應

氧化反應有分為乾氧化和濕氧化。乾氧化是氧化層成長於無水氣的乾氧下:

Si+O2. SiO2

其反應時間和量是與晶圓表面上的氧純度和反應溫度有關,反應速率隨溫度增加而增加。濕氧化有水蒸氣參與反應,氧化反應速率快速增加,比乾氧化快:

Si+2H2O SiO2+2H2

但產生的氫氣會被SiO2捕捉,使氧化層的密度較乾氧化產生的低,藉由加熱可改善結構和性質,變得和乾氧化氧化層相似。

4.1.3 氧化成長模型(oxidation growth model)

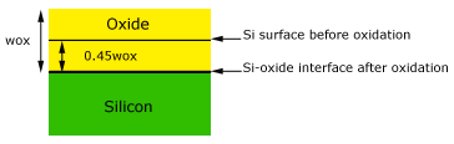

乾、濕氧化都會消耗原本的矽,消耗的厚度是二氧化矽層的45%左右。另外,氧化過程因二氧化矽隔離氧和矽,需要使氧擴散穿透到晶圓的矽才會開始成長氧化層。

圖十二:氧化成長模型

4.2 沈積(deposition)

4.2.1 薄膜專門用語

4

1. 多層金屬化(multilevel metallization)

指連接晶圓上高密度金屬與介電層,金屬層間是已介電層薄膜中的開口(vias)連接。

![EE143 – Ali Javey Section 8: Metallization Jaeger Chapter 7. - [PPT Powerpoint]](https://jackeyliutw.github.io/wp-content/uploads/2021/07/Picture1-1.png)

圖十三:多層金屬化

2. 金屬層

鋁金屬化(aluminum metallization)是沈積鋁金屬固態薄膜在蝕刻出寬度、間距。用metal-1,metal-2稱每一層。臨界層(critical layers)的線寬就是臨界尺寸,對污染、電遷移敏感。

3. 介電層

矽主動元件和metal-1之間的介電質稱為第一介電質(first interlayer dielectric, IDL-1), IDL-1的功用是對金屬內連線層作電性隔離和對可移動離子之污染源作物理性隔離。IDL傳統是用SiO2,介電系數3.9~4。

4.2.2 薄膜沈積

薄膜非常薄,遠薄於基板。製作薄膜有三種重要特性:

1. 薄膜階梯覆蓋(film-step coverage)

薄膜需要表面厚度均勻,若薄膜超出階梯太多會導致高應力、電性短路或不希望產生的感應電荷。

圖十四:階梯覆蓋

2.高深寬比間隙(high aspect ratio gap)

能填的深寬比高,能填滿越深越窄的洞,如介電質的介電孔和淺溝渠(STI)。

圖十五:高深寬比間隙

3. 厚度均勻(good thickness uniformity)

類似階梯覆蓋。

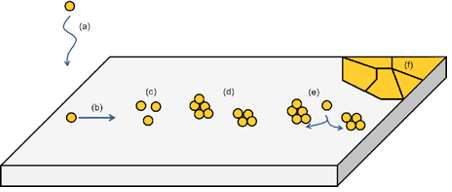

4.2.2 薄膜成長(film growth)

薄膜成長有三個步驟。

1. 成核(nucleation),即形成穩定核團,原子或分子結合成小塊狀。

2. 塊狀核團晶粒聚結(nuclei coalescence),稱為島成長(island growth)。任意方向的島核團成長是和表面移動率和合團密度有關。

3. 連續薄膜(continuous film),沿著基板表面延伸形成固態薄膜。

圖十六:薄膜成長

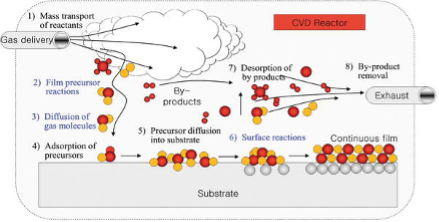

4.2.2 化學氣相沈積(chemical vapor deposition, CVD)

化學氣相沈積是藉由氣體混合物之化學反應在晶圓表面上沈積固態薄膜,效果比物理氣相沈積好,有較高深寬比。

圖十七:薄膜成長

4.2.2 物理氣相沈積(physical vapor deposition)

可分成兩類:蒸鍍(evaporation)、濺鍍(sputtering)蒸鍍主要用於金屬,用電子束(incident electron beam)加熱樣板。置放欲沉積的材料於坩鍋中在真空

6

加熱到蒸發。

圖十八:蒸鍍

濺鍍是以在高真空反應室的電漿中產生的氬離子撞擊高純度固體面靶材,將其原子物理性擊出,沈積於晶圓。

圖十九:濺鍍

4.3 微影(photolithography)

微影用光敏的光阻,控制其曝光量以產生三維圖案。

4.3.1 微影製程

微影製程可分為正雕像和負雕像,正雕像是用正光阻,正光阻照光鍵結會被破壞,形成的圖案會和標線版上的相同。負雕像是用負光阻,負光阻原本無鍵結,照光後才會產生鍵結,形成的圖案會和標線版上的相反。

4.3.2 微影步驟

1. 氣相塗底(vapor prime)

先清洗、去水後,以Hexamethyldisilane(HMDS)塗底。

2. 旋轉塗佈

上液態光阻,晶圓底部以真空吸附旋轉塗佈。

3. 軟烤(soft bake)

進入軟烤,去除大部分溶劑,改善附著性,提升光阻均勻性,以獲得較佳線寬。程序是將晶圓放在熱墊板上加熱,溫度90~100°C,加熱30秒。

4. 對準及曝光(alignment & exposure)

將光罩對準並曝光。

5. 曝光後烘烤(post-exposure bake)

光阻曝光後再熱墊板上加熱100~110°C,這對深紫外光(DUV)製程是必須的。

6. 顯影(develop)

使圖案顯現。用液態顯影的化學物質溶解可溶解的光阻,再浸入去離子水,在旋乾。

7. 硬烤(hard bake)

顯影後烘烤。使剩餘光阻溶劑揮發,提升附著力。溫度120~140°C。

8. 顯影後檢視

檢查,有問題就去除光阻重做。

圖二十:微影步驟

4.4 顯影(develop)

顯影是用顯影劑洗掉因被曝光而改變結構性質的光阻。

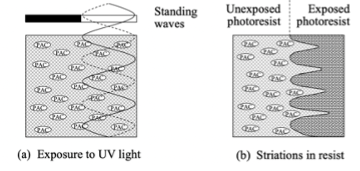

4.4.1 曝光後烘烤(post-exposure bake, PEB)

曝光後烘烤對化學放大(chemical amplify)的DUV光阻是必要的,以活化光阻的化學反應,對傳統的DNQ化學品的i-line光阻而言,PEB可改善黏著度和減少駐波效應。減少駐波效應是因溫度增加使光阻中的 PAC sensitizer從novolak高分子聚合物裡擴散出來,在駐波邊界產生平均效應。

圖二十一:平均效應

7

4.4.2 顯影問題

1. 欠顯影(underdevelopment):線寬比正常大,呈現傾斜式側壁。

2. 未完成顯影:在基板殘留應移除的光阻。

3. 過顯影:過度移除光阻,特徵尺寸變窄且圖案不佳。

4.5 蝕刻(etch)

顯影是去除光阻,蝕刻是除掉沒被光阻覆蓋的地方,用化學或物理手段從晶圓表面選擇性移除。

4.5.1 蝕刻方法

1. 乾蝕刻:將暴露於氣體狀態中的電漿通過光阻開口,與晶圓做物理、化學反應,而移除材料。較濕蝕刻好控制臨界尺寸、較少光阻剝離或附著性問題、均一性好、低善後成本。

2. 濕蝕刻:用酸鹼溶劑的液態化學品蝕刻,用於大於三微米的尺度。

4.5.2 蝕刻速率

代表蝕刻期間從晶圓表面移除材料的速率,正比於蝕刻劑的濃度。蝕刻面積大會稀釋濃度,速率變慢,蝕刻面積小,速率快,此現象稱負載效應。

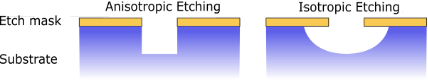

4.5.3 蝕刻輪廓(etch profile)

1. 等向性(isotropic):在所有方向都以相同速率蝕刻,會讓線寬失真。

2. 異向性(anisotropic):蝕刻只發生在垂直晶圓表面的方向。

濕蝕刻只能做等向性蝕刻,乾蝕刻則兩者皆可。物理性蝕刻是用電漿提供正電子,用電場加速朝向晶圓表面撞及,產生異向性蝕刻。化學性蝕刻是利用原子團在液態中和晶圓表面作用,產生等向性蝕刻。

圖二十二:蝕刻輪廓

4.6 參雜參雜是將半導體晶體參入參質,改變半導體電性。參雜有兩種方法:

1. 熱擴散(thermal diffusion):用高溫將參質擴散進矽晶格。

2. 離子植入(ion implantation):透過高電壓離子轟擊,將參質導入基板。植入後須馬上退火以活化晶體中的參質離子,所有製成都在高真空環境實施。相較於熱擴散,在寬廣濃度範圍,均能有精確控制植入參質數目的能力,且均一性佳、參質穿透深度控制良好、低溫製程,缺點是高能離子進入晶體並和基板碰撞時,有的矽原子從晶格中錯位,稱輻射損壞(radiation damage),可用高溫退火修復。

4.6.1 參質運動

1. 晶隙移動(interstitial movement):在晶格間隙空間移動。

2. 置換移動(substitutional movement):取代原本原子的位置移動。

圖二十三:參質運動

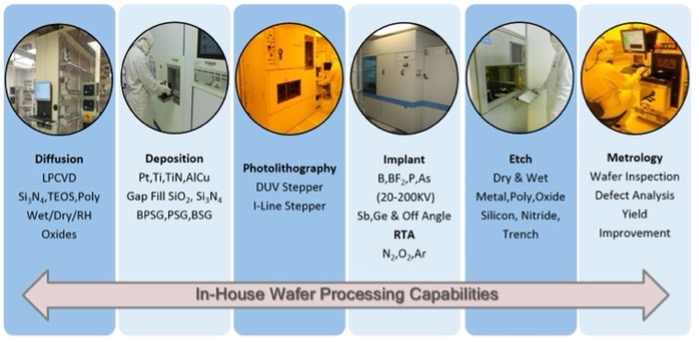

5. 晶圓廠製造區域

大致可將晶圓廠製造區域分為六個區域,分別是擴散區(diffusion)、微影區(photolithography, 又稱黃光區)、蝕刻區(etch)、離子植入區(ion implant)、薄膜區(thin film)、研磨區(polish)。

1. 擴散區(diffusion):

進行高溫製程、薄膜沈積、成長氧化層。

2. 微影區(photolithography, 又稱黃光區):

此區採用黃光螢光燈管照明,因為光阻對紫外光和日光敏感,有光阻塗布/顯影機(coater/developer track),且必須保持極度乾淨以免微粒吸附上光阻。

3. 蝕刻區(etch):

有電漿蝕刻機(plasma etcher, 有真空室, 用射頻能量使氣體分子解離)、電漿去光阻機(plasma resist stripper)、濕式清洗台。4. 離子植入區(ion implant):

8

在此將高能參質如:砷、磷、硼等離子氣體打入。

5. 薄膜區(thin film):

此處進行沈積介電質和金屬主要是化學氣相沈積。

6. 研磨區(polish):

使用化學機械平坦化機制(chemical mechanical planarization)使表面平坦。

圖二十四:晶圓廠製造區域劃分

6. 參考文獻

- https://tinyurl.com/dj9r7yk8

- Ni,S.;Yu,Q.;Hung,Y.;Wang,J.;Li,L.;Yu,C.Heterostructured TiO2/MgO nanowire arrays for self-powered UV photodetectors. RSC Adv. 2016, 6, 85951–85957.

- https://tinyurl.com/fhjpnyew

- https://tinyurl.com/hx7kt2a3

- Kim,D.;Shin,G.;Yoon,J.;Jang,D.;Lee,S.J.;Zi,G.;Ha,J.S.High performance stretchable UV sensorarrays of SnO2 nanowires. Nanotechnology 2013, 24, 315502.

- https://tinyurl.com/3pbajwbj

- https://tinyurl.com/2ebzw53n

- Park,J.;Lee,J.;Noh,Y.;Shin,K.H.;Lee,D.Flexible ultraviolet photodetectors with ZnO nanowire networks fabricated by large area controlled roll-to-roll processing. J. Mater. Chem. C 2016, 34, 7948–7958.

- https://tinyurl.com/9xa8wbew

- https://tinyurl.com/a8bkp2h4

- https://tinyurl.com/5cehmtz9

- https://tinyurl.com/ray93bwu

- Zeng,Y.;Pan,X.;Lu,B.;Ye,Z.Fabricationofflexibleself-poweredUVdetectorsbasedonZnOnanowires and the enhancement by the decoration of Ag nanoparticles. RSC Adv. 2016, 6, 31316–31322.

- https://tinyurl.com/mddaf6w9

- https://tinyurl.com/axh7nv4f

- https://tinyurl.com/2xceta83

- https://tinyurl.com/24nn4m7t

- Sung-Mo Kang, Yusuf Leblebici著,吳紹懋,黃正光編譯,「CMOS數位積體電路分析與設計」全華科技圖書,台北,民國93年。

- https://tinyurl.com/vshbwz38

- https://tinyurl.com/24fzhkx9

Patel,D.B.;Patel,M.;Chauhan,K.R.;Kim,J.;Oh,M.S.;Kim,J.W.High-performing flexible and transparent photo detector

- by using silver nanowire-networks. Mater. Rese. Bull. 2018, 97, 244–250.

- https://tinyurl.com/448ryev8

- https://tinyurl.com/22nmbnvd

- Reshchikov,M.A.;Morkoç, H.Luminescence properties of defectsin GaN.J.Appl.Phys.2005,97,061301.

- https://tinyurl.com/ynyb2bne

- https://tinyurl.com/462ff6tf

- Kim, H.W.; Shim, S.H. Synthesis and characteristics of SnO2 needle-shaped nanostructures. J. Alloys Compd. 2006, 426, 286–289.

- https://tinyurl.com/925xmzv

- H. H. Wang, C. W. Hsu, W. H. Liao, L. J. Yang and C. L. Dai, “Micro pressure sensors of 50 um size fabricated by a standard CMOS foundry & a novel post process”, Proceedings of IEEE International Conference on Micro Electro Mechanical Systems, pp.578-581, 2006.

- https://tinyurl.com/83fe8nv5

- https://tinyurl.com/ykf64mvp

- Cao, B.Q.; Matsumoto, T.; Matsumoto, M.; Higashihata, M.; Nakamura, D.; Okada, T. ZnO Nanowalls Grown with High-Pressure PLD and Their Applications as Field Emitters and UV Detectors. J. Phys. Chem. C 2009, 113, 10975–10980.

- https://tinyurl.com/7kppy43j

- www.cic.edu.tw,國家晶片系統設計中心網站。

- https://tinyurl.com/2k7twuzx

- https://tinyurl.com/mrysak2h

- S. Hafizovic, F. Heer, W. Franks, F. Greve, A. Blau, C. Ziegler, A. Hierlemann, “CMOS bidirectional electrode array for electrogenic cells,” Proceedings of the IEEE International Conference on Micro Electro Mechanical Systems, pp.4-7, 2006.

© 2021 by the authors. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

View backup on Ethereum blockchain:

0xd16c3ccd84f345a2e11a3cdc986934f75083e26bb9e35bb21ca9de166904f07f

9

Loading…

Loading…